Hi

everyone,

I know that

my question is a bit inappropriate when writing here, but I

submitted on the Mathlab Community but no one helped.

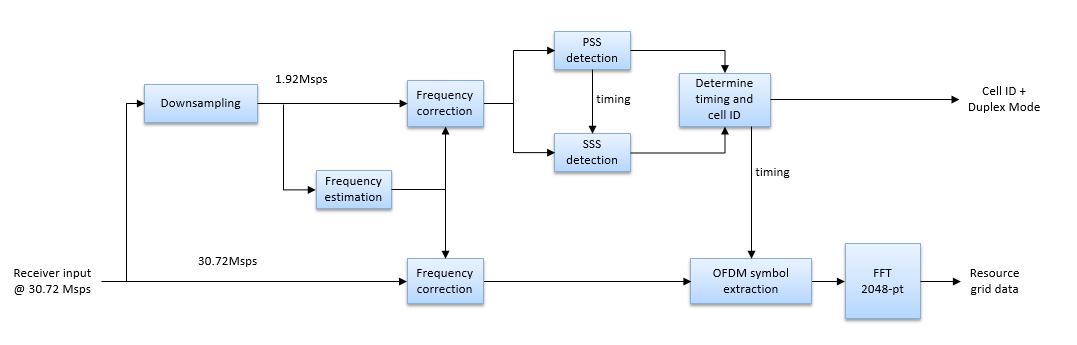

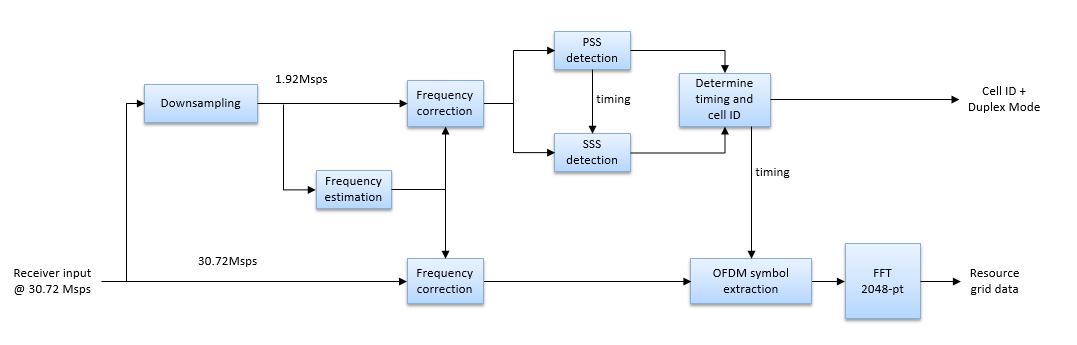

I'm working with LTE HDL Cell Search example of Matlab to generate VHDL code. (LTE HDL Cell Search), and then wrap the VHDL code to RFNoC Block and connect them following diagram: Radio -> DDC -> Cell Search Block -> GNU Radio

After

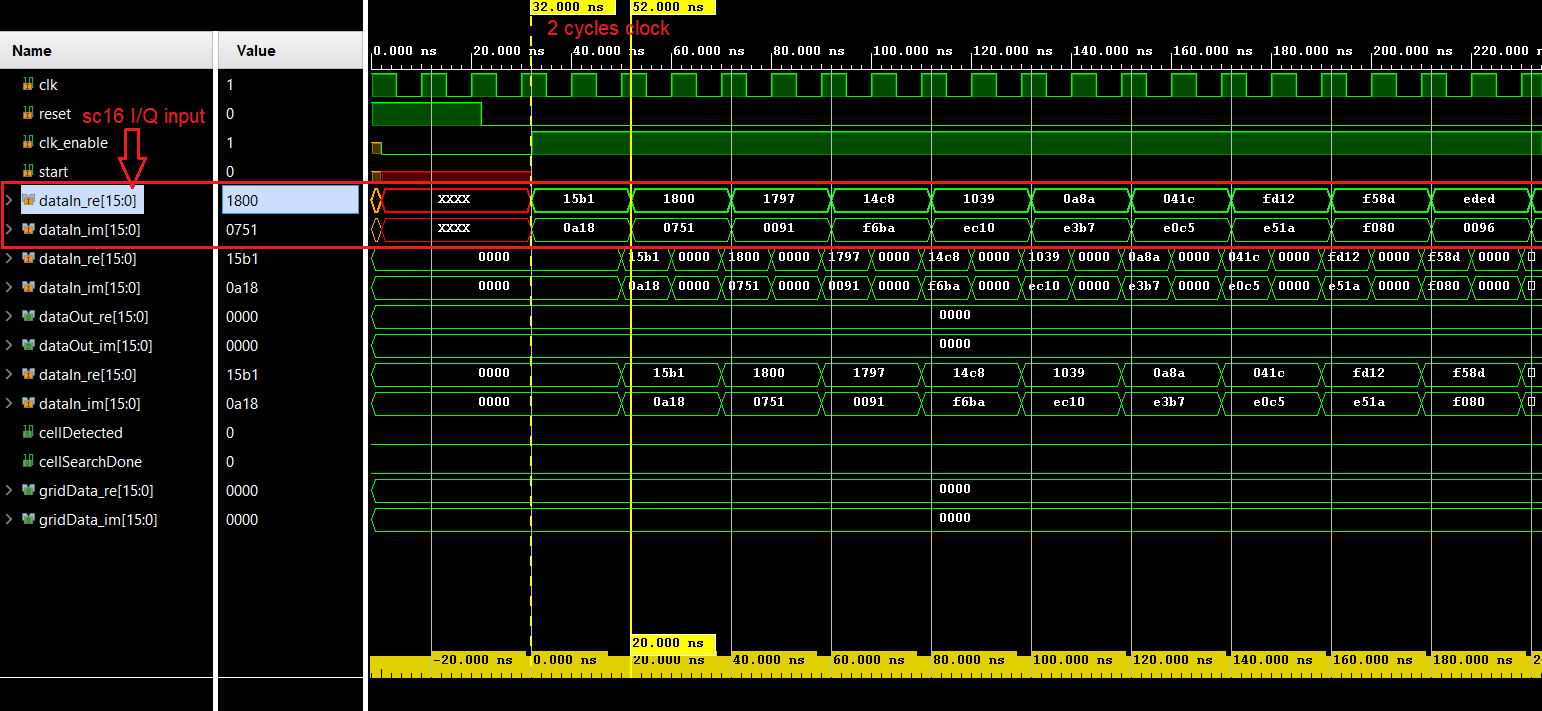

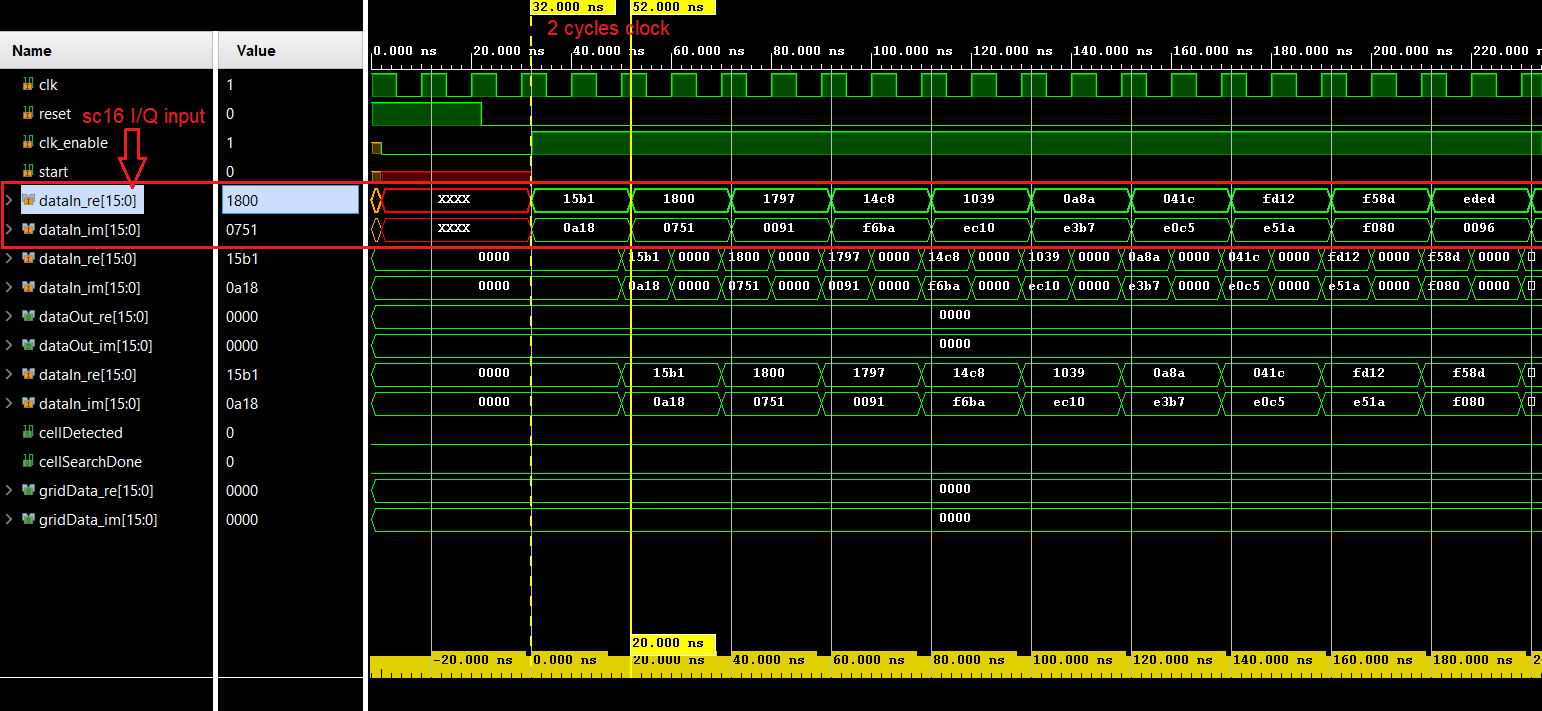

generating the VHDL code from Matlab (including simulation

code), when running the simulation on Vivado, I see that every sample at the input takes 2 cycles of clock like the image below. When I change each sample by 1 cycle clock, the block did not work.

The document said that the input sample rate is 30.72 Msps, I understand that 30.72 Msps is the sample rate of ADC and different with clock rate, it makes me a little bit confused about why the sample takes 2 cycles clock here because in the actual case, it takes only 1 cycle clock?

Please someone help me with my problem?

Thank you so much!